Un sistema síncrono sólo procesa las señales de las entradas en unos instantes determinados. Estos instantes vienen determinados por la señal periódica de reloj (CLK). Los dos tipos de sincronismo que vamos a encontrar son:

- Sincronismo por nivel. Cuando el reloj está en nivel activo, el sistema secuencial procesa las señales de entrada.

- Sincronismo por flancos. En el instante en que se produce un cambio en el reloj, ya sea de flanco de subida (↑) o de bajada (↓), se procesan las señales de entrada.

Biestables síncronos por nivel

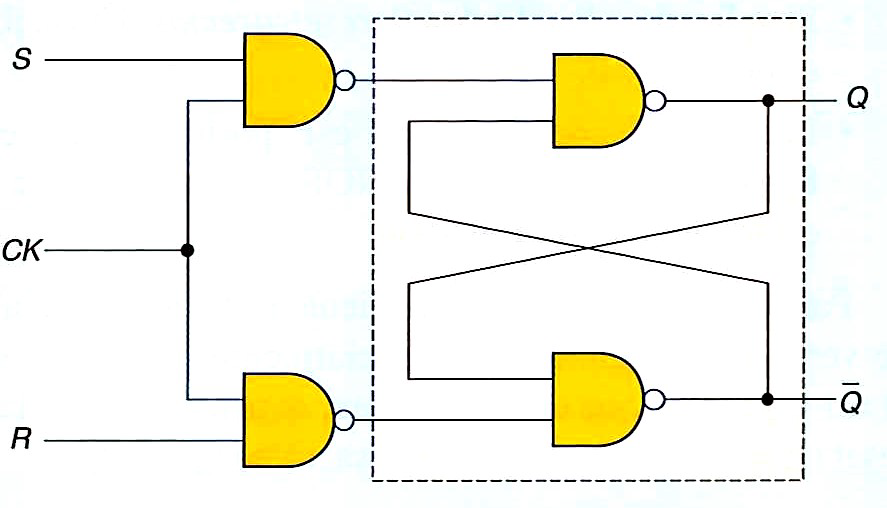

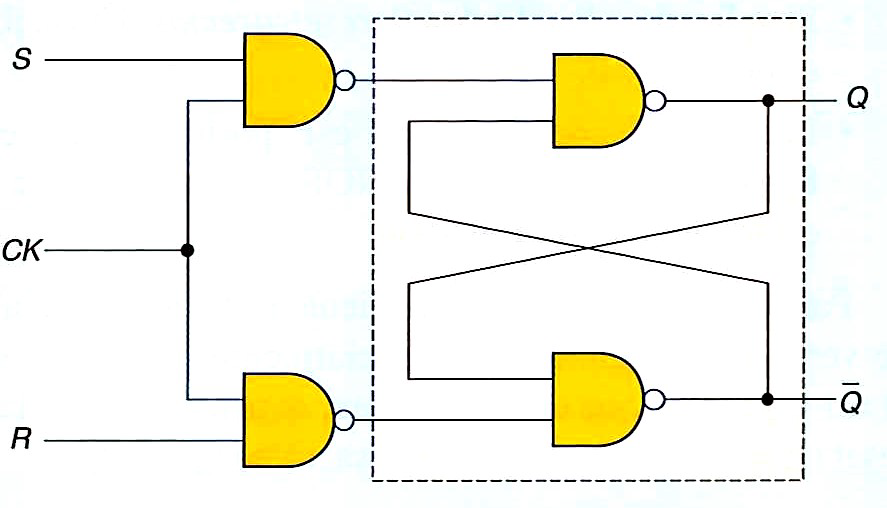

Un biestable RS síncrono se obtiene a partir de uno asíncrono, añadiendo en cada una de las entradas de disparo una puerta lógica gobernada por la señal de reloj (señal CK). Para el caso del biestable RS asíncrono en puertas NAND obtendremos el circuito de la figura.

Veamos cómo funciona:

- Durante el nivel alto de la señal de reloj (CLK 1) el valor de las entradas de disparo R y S pasa al interior del circuito (formado por el biestable RS asíncrono); fíjate que las entradas pasan al interior como Ŝ y Ř, tal y como se ha visto para este biestable RS en puertas NAND. Los valores de salida del biestable dependerán de la combinación RS durante este nivel alto de la señal de reloj.

- Durante el nivel bajo de la señal de reloj (CLK a 0) en las entradas del biestable RS asíncrono tendremos un 1 en cada una, y para esta combinación ya hemos visto que las salidas mantienen su estado (no cambian).

En este tipo de biestables, las entradas de disparo pasan a llamarse entradas síncronas, ya que están gobernadas por la señal de reloj. El biestable RS síncrono de la figura es un biestable sincronizado por nivel (en este caso por nivel alto), ya que es en este nivel cuando el biestable puede cambiar sus salidas, permaneciendo inalterable a las combinaciones de entrada cuando el reloj está a nivel bajo. A estos biestables también se les suele denominar biestables activos por nivel. En los biestables activos por nivel, éste puede ser el nivel alto o nivel bajo.

Biestables síncronos por flancos.

En muchas situaciones es necesario sincronizar el funcionamiento de muchos circuitos diferentes y resulta de utilidad poder controlar el momento en el que un circuito cambiará de estado. Algunos biestables están construidos de manera que sólo cambian de estado ante la aplicación de una señal de disparo, en concreto ante el flanco de bajada o de subida de una señal de entrada llamada reloj (CLK). Estos biestables reciben el nombre de biestables disparados por flanco, o más comúnmente flip-flops. El término síncrono significa que la salida cambia de estado únicamente en un instante específico de una entrada de disparo (reloj), es decir, los cambios en la salida se producen sincronizadamente con el reloj.

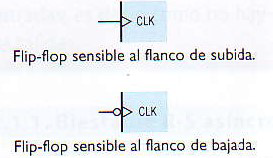

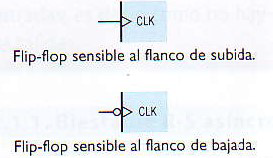

Podemos encontrar dos tipos de flip-flops:

- Los que son disparados por el flanco de subida de la señal de reloj.

- Los que son disparados por el flanco de bajada de la señal de reloj.

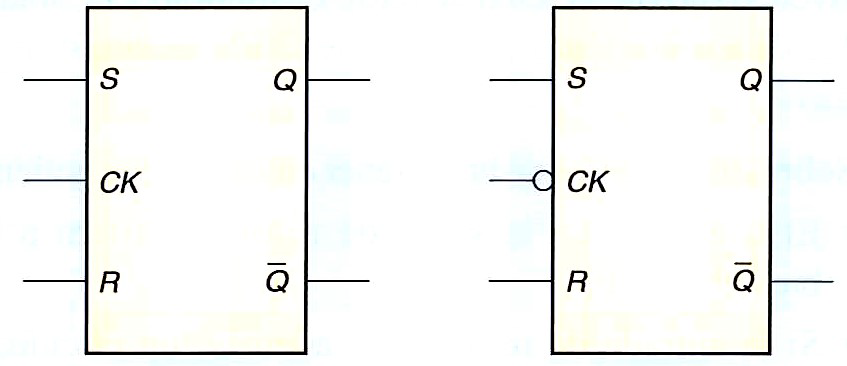

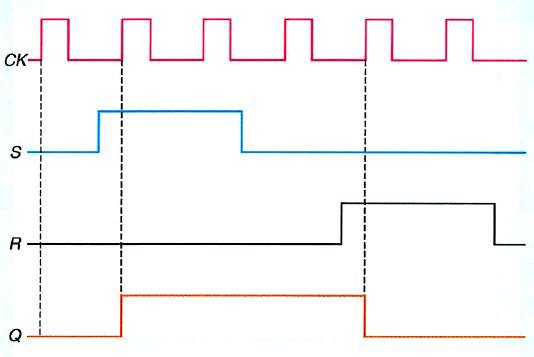

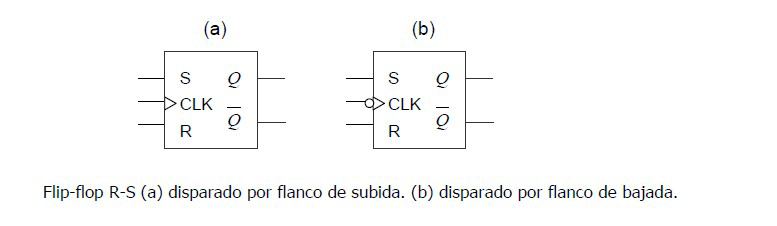

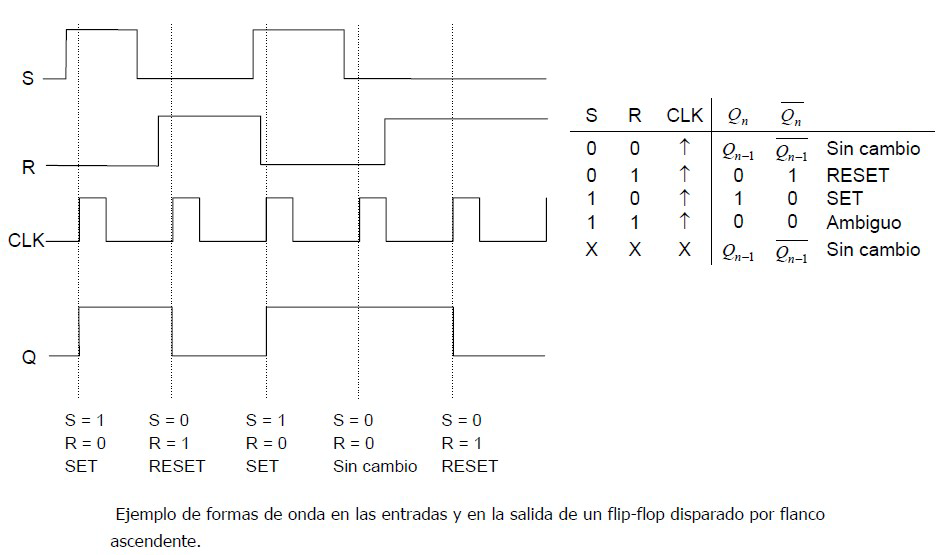

Biestable S-R disparado por flanco.

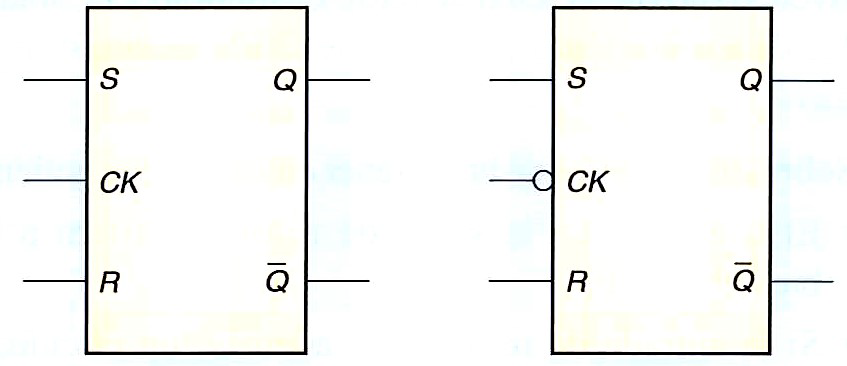

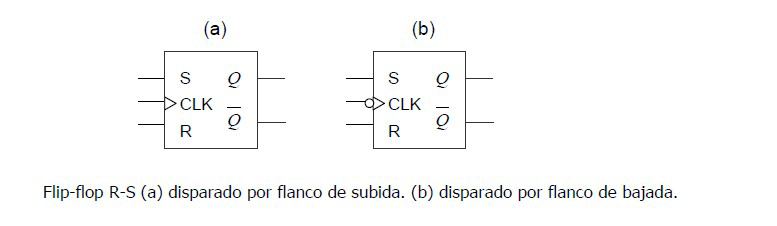

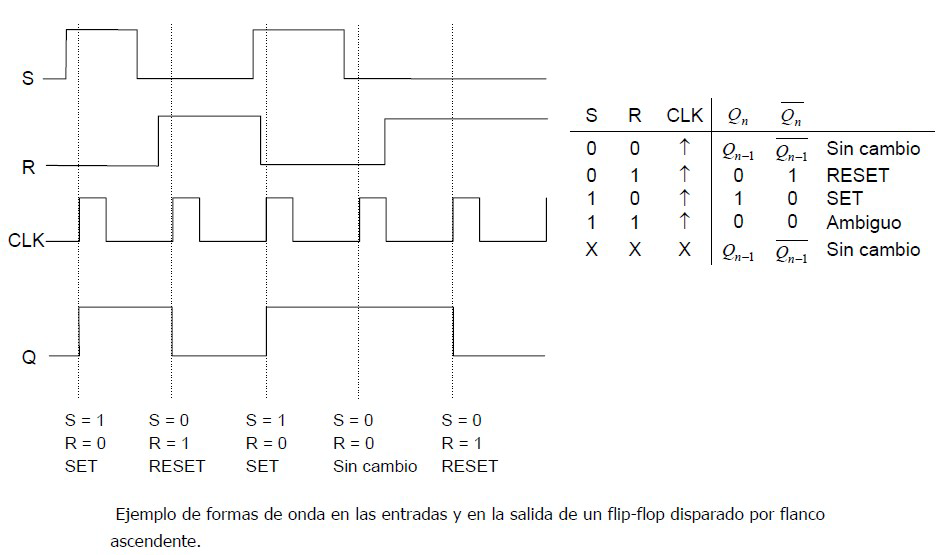

Se asemeja al biestable R-S excepto en que el circuito sólo responde a sus entradas en el flanco ascendente o descendente de la señal de reloj. Los símbolos gráficos de la figura se asemejan a los de los biestables con entrada de habilitación, excepto en que esta última entrada se reemplaza por una entrada de reloj.

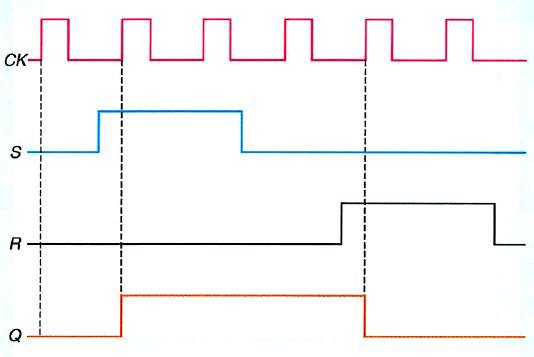

En ausencia de la transición de reloj el flip-flop permanece en su modo de memoria, como se aprecia en el diagrama de la figura, correspondiente a un flip-flop disparado con flanco de subida.

El funcionamiento de un flip-flop R-S activado por flanco descendente es, por supuesto, idéntico, excepto que el disparo tiene lugar en el flanco de bajada de la señal de reloj (cuando cambia de ‘1’ a ‘0’).

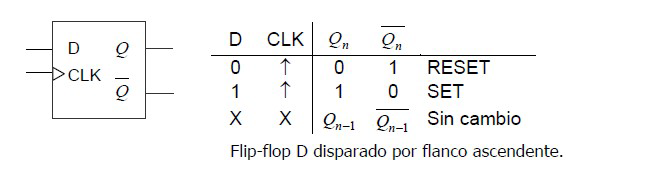

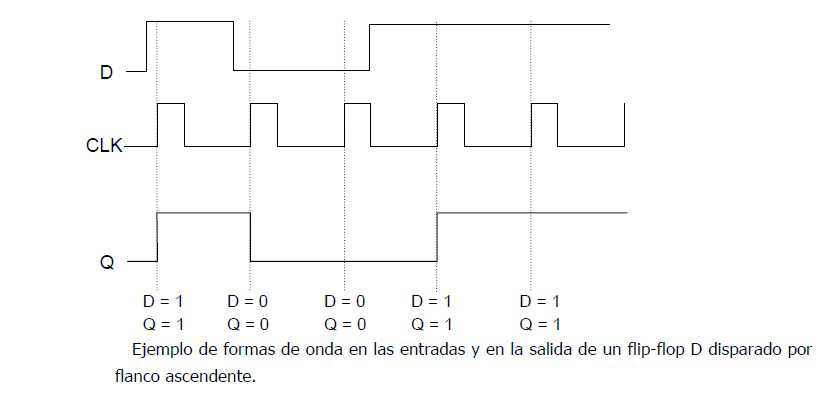

Flip-flop D disparado por flanco.

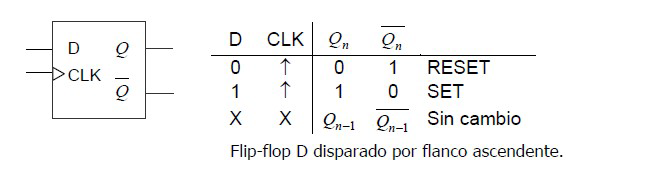

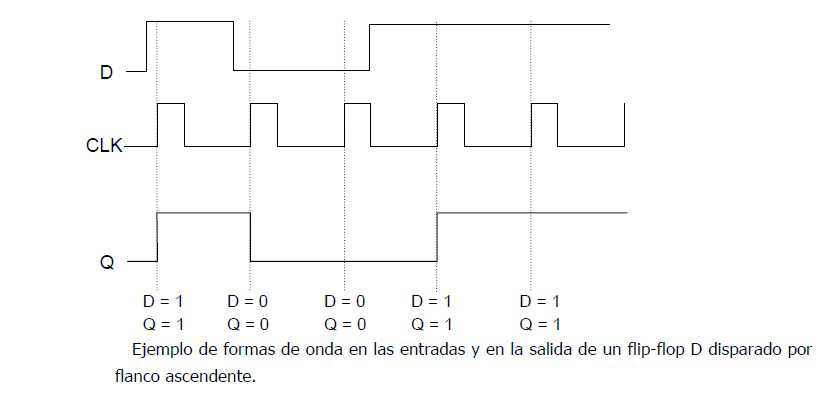

Su comportamiento es similar al del latch D descrito con anterioridad, la salida del flipflop tipo D se igualará a la entrada en el instante en el que se produzca el flanco ascendente o descendente (según el tipo de flip-flop) de la señal de reloj (CLK). En la figura se observa el símbolo lógico y la tabla de verdad de un flip-flop tipo D disparado por flanco ascendente. El funcionamiento de un flip-flop D disparado por flanco ascendente se resume en la figura:

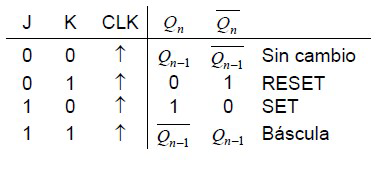

Flip-flop J-K disparado por flanco.

El flip-flop J-K se comporta como el flip-flop R-S a excepción de que resuelve el problema de tener una salida indeterminada cuando las entradas se encuentran activas a la vez. La entrada J es la equivalente a la entrada S de un flip-flop R-S y la entrada K, al equivalente a la entrada R. En este dispositivo cuando las dos entradas se colocan a nivel alto la salida cambia al estado opuesto al que se encontraba. A este modo de funcionamiento se le denomina modo de basculación.

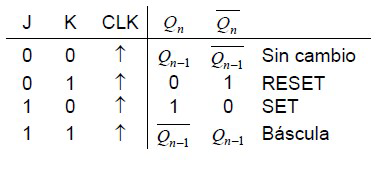

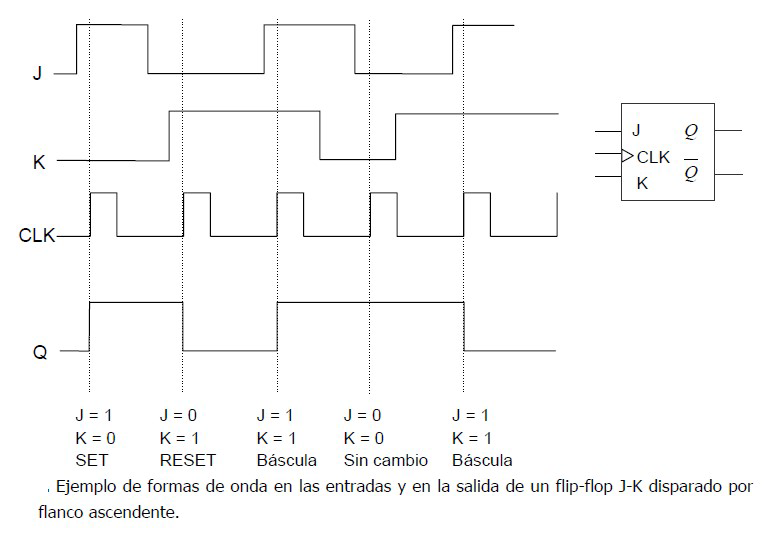

La tabla de transición muestra las características de un flip-flop J-K disparado por flanco ascendente. La figura ilustra el funcionamiento del flip-flop J-K disparado por flanco ascendente y su símbolo lógico. El flip-flop J-K es uno de los flip-flops más ampliamente utilizados.

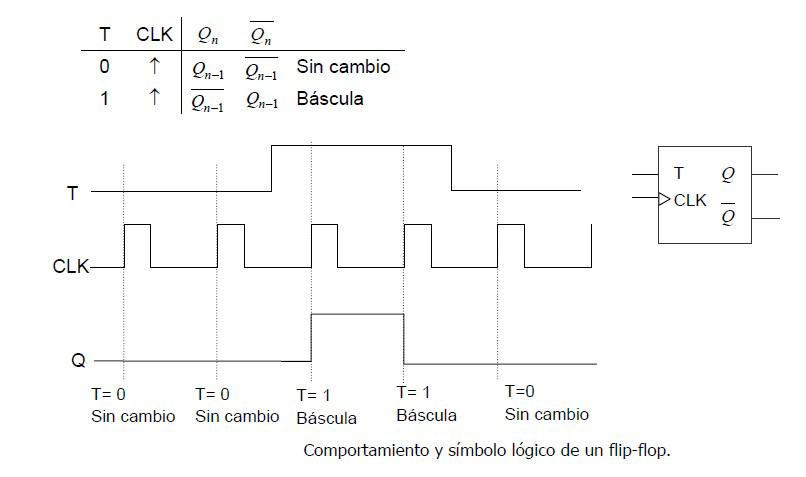

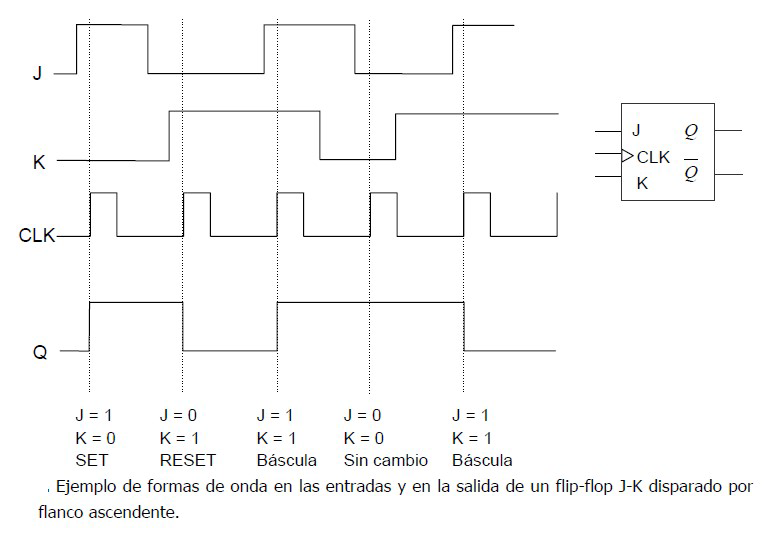

Flip-flop T.

Existe otro tipo de flip-flop con una única entrada (T). El comportamiento de un flip-flop tipo T es equivalente al de un flip-flop tipo J-K con sus entradas J y K unidas. De este modo, si la entrada T presenta un nivel bajo ‘0’ el dispositivo está en su modo de memoria, y si al entrada T se encuentra a nivel alto ‘1’ el dispositivo cambia de estado, es decir la salida bascula. En la figura se aprecia este comportamiento y el símbolo lógico.