Las operaciones aritméticas fundamentales (suma, resta, multiplicación y división) se pueden realizar con códigos binarios mediante circuitos lógicos combinacionales, construidos a partir de su correspondiente tabla de verdad.

En este apartado trataremos únicamente de la suma y de la resta y sólo para el caso de números enteros.

Suma aritmética

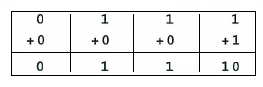

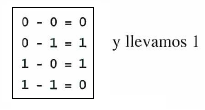

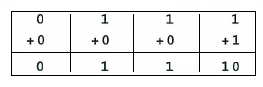

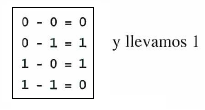

Consideraremos inicialmente la suma de dos números de un solo bit cada uno:

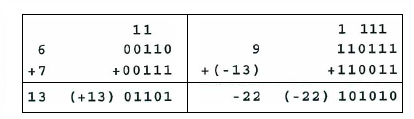

Como se puede observar, cuando sumamos 1+1 el resultado es 0 y nos llevamos 1 (en decimal la suma se representaría como 2 y es lo que, en realidad, representamos con 10). Cuando se produzca una suma en la que nos llevamos algo, decimos que se produce acarreo, y al bit correspondiente le llamamos bit de acarreo (como el 1 de la suma 1+1). Veamos algunos ejemplos de sumas:

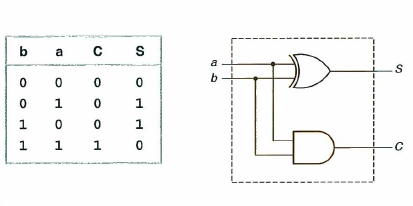

Semisumador

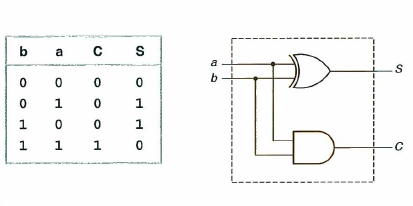

A continuación diseñaremos el circuito que realiza la suma de dos números de un bit cada uno, partiendo de su tabla de verdad. El circuito tiene dos entradas (a y b) y dos salidas: una obtiene la suma (S) y la otra el acarreo (C). Tabla y circuito se muestran en la figura:

Las funciones lógicas suma y acarreo se obtienen directamente de la tabla de verdad:

El circuito que realiza la suma de dos números de un solo bit se denomina semisumador.

Sumador completo

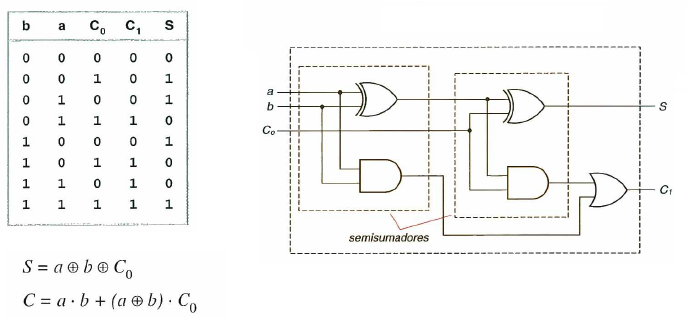

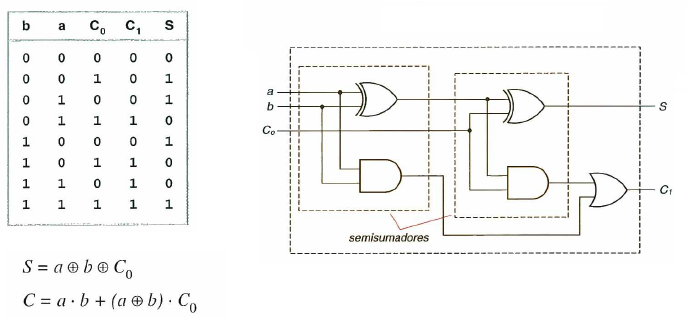

Para sumar números de más de un bit, como los utilizados en los ejemplos anteriores, se utiliza un sumador denominado sumador completo o total (ver figura). Este sumador tiene en cuenta el posible acarreo inicial (que se sumaría a la suma de los dos bits de menor peso), lo que supone contar con una entrada más). La tabla de verdad del se muestran en la tabla siguiente:

El bloque sumador completo de la figura presenta las siguientes entradas y salidas:

- Dos entradas, una para cada bit (a y b), para los dos números que queremos sumar.

- Una entrada de acarreo inicial (C0) por la que se introducirá el acarreo producido en una suma anterior.

- Dos salidas: el resultado de la suma de los dos bits (S) y el posible acarreo producido en esa suma (C1).

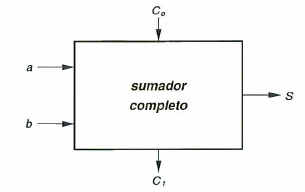

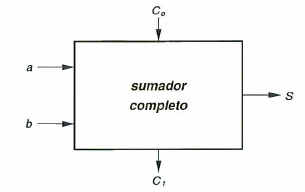

El bloque sumador completo quedaría como sigue:

Sumadores de n bits

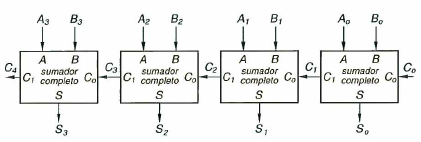

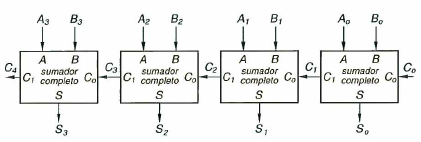

La conexión en cascada de varios sumadores completos permite la suma de dos números binarios de varios bits cada uno. Un ejemplo de ello es el sumador de 4 bits, como el integrado en el chip 7483:

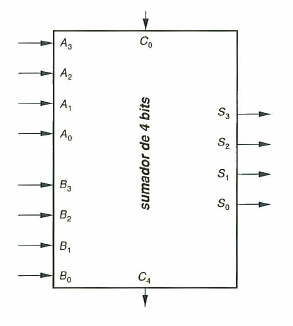

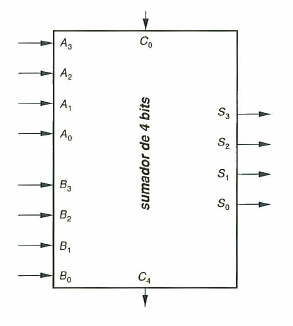

En bloque funcional sería así:

Del sumador de 4 bits podemos indicar:

- Puede sumar dos números binarios de cuatro bits cada uno: A (A3,A2,A1,A0) y B (B3,B2,B1,B0,).

- El acarreo inicial del sumador (C0), para una suma de dos números de 4 bits cada uno, es 0.

- Genera un acarreo de salida (C4) que permite utilizar este sumador como un solo bloque que se puede, a su vez, conectar en cascada con otro bloque idéntico para formar un sumador binario de 8 bits, y así sucesivamente, uno de 16, 32 y más bits.

Resta binaria

La resta binaria se realiza de forma similar a la suma binaria:

Los circuitos digitales realizan la resta binaria de dos números sumando el primer número con el opuesto del segundo. Esta suma se realiza bit a bit, incluyendo el bit de signo y despreciando el acarreo final (el bit superior al bit de signo). Los circuitos digitales que realizan esta operación son los ya conocidos sumadores de n bits.

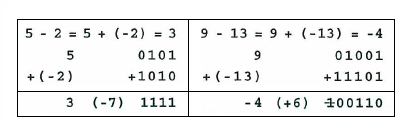

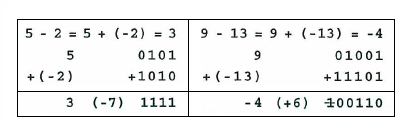

Como ya se ha comentado, para esta operación de resta binaria los números no pueden estar representados en VAS ya que, como se ve en los dos siguientes ejemplos, el resultado es erróneo:

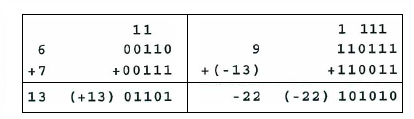

La resta de dos números se realiza en C-2, y, lógicamente, el resultado queda también en C-2. Hay que recordar cómo se obtiene el opuesto de un número dado en C-2: se complementa a 2 todo el número, incluido el bit de signo (utilizando la regla práctica). Repetimos las dos restas anteriores, representando ahora los números en C-2:

Sobre estas dos últimas restas hacemos las siguientes consideraciones:

- En la primera (5 — 2 = 3) se produce un acarreo final que no se debe tener en cuenta. Lo mismo ocurre en la operación 9 — 13 de los números dados en VAS.

- En la segunda resta (9 — 13 = -4) el resultado es negativo y viene dado en C-2. Para comprobar que es correcto deberemos pasarlo a VAS dado que en este sistema reconocemos mejor los números. Para ello, no hay más hacer el complemento a 2 del número excluido el bit de signo (ya que no estamos hallando el opuesto, sino convirtiendo de un sistema a otro):

11100C-2> 10100(4).

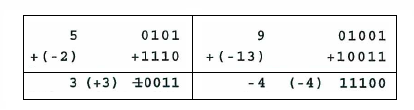

El acarreo que se produce en la suma de números representados en C-2 se debe interpretar de la siguiente forma:

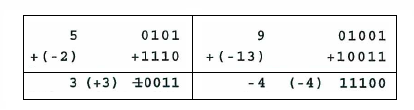

- Si los signos de los números que se suman son diferentes, el acarreo obtenido es falso y no se debe tener en cuenta, como en el ejemplo de 5 + (-2).

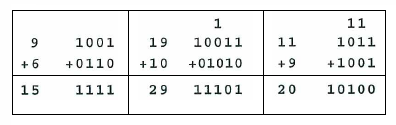

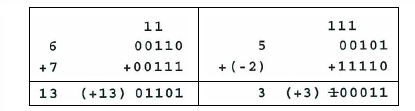

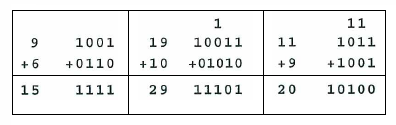

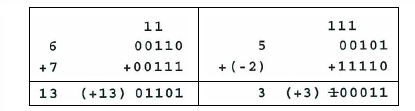

- Si los signos de los números que se suman son iguales, el acarreo es verdadero y actúa como el bit de signo. Si no se produce acarreo se considera que éste es 0 y el resultado es positivo. Veamos dos ejemplos:

En realidad, el acarreo se produce cuando el resultado requiere más bits que los que se están usando en la operación. En la suma de 6 y 7, ambos representados con 3 bits más el de signo, el resultado (13) necesita 4 bits más el de signo. Lo mismo ocurre en la otras suma de números negativos.

La solución más práctica para evitar el acarreo es utilizar un bit más que los estrictamente necesarios y despreciar siempre el acarreo final. Veamos nuevamente las operaciones anteriores: